Xilinx©'s next-generation design suite, Vivado, introduces a new constraint file, XDC, which is quite different from the UCF supported in the previous generation ISE in many rules and techniques, presenting many additional challenges for users. Xilinx tool experts tell you that it's easy to use XDC well, just master a few core tricks, and always keep in mind that the syntax of XDC is actually the Tcl language.

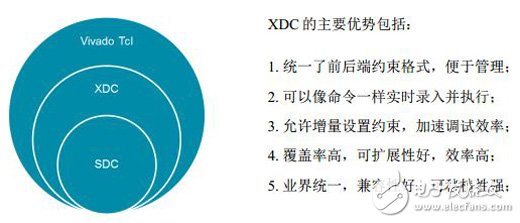

The advantages of XDCXDC is short for Xilinx Design Constraints, but its basic syntax comes from the industry's unified constraint specification SDC (originally proposed by Synopsys, hence the name Synopsys Design Constraints). So the relationship between SDC, XDC and Vivado Tcl is shown below.

XDC is essentially the Tcl language, but it only supports basic Tcl syntax such as variables, lists, operators, etc. For other complex loops and file I/O syntax, you can source a Tcl file in Vivado. supplement. (For readers interested in Tcl topics, see the author's other article, "Application of Tcl in Vivado.") The main difference between XDC and UCF is twofold:

1. The XDC can be read as a whole file as a UCF file, or it can be executed directly as a separate command during the implementation process. This determines that the XDC also has the characteristics of the Tcl command, that is, the constraints entered later will override the previously entered constraints in case of conflicts (the priority of the timing exception will be detailed in the next section). In addition, unlike UCF, which is all read and reprocessed, in XDC, the constraint is to read one execution, so the order is very important. For example, before setting the IO constraint, the corresponding clock must be created first.

2. UCF is completely from the perspective of FPGA, so the default is that all clocks are synchronized unless they are pre-declared, otherwise they are treated as asynchronous without cross-clock domain timing analysis; XDC is the opposite, the blood background of ASIC world It is decided that all the clocks are considered to be fully synchronized by default. In the absence of timing exceptions, the tool will actively analyze each path across the clock domain.

Basic syntax of XDCThe basic syntax of XDC can be divided into three categories: clock constraints, I/O constraints, and timing exception constraints. According to the recommendations of the Baseline part of Xilinx's UltraFast design methodology (described in detail in UG949), the order in which constraints are imposed on a design can also be followed in accordance with these three types of constraints. This article does not explain the basic XDC syntax that can be found in the help documentation, and will focus on how to use it.

Clock constraint The clock constraint must be created earliest. For 7 series FPGAs, the incoming master clock and the GT output RXCLK/TXCLK must be created by the user using create_clock. The derived clocks are divided into the following two categories:

The output clocks of the MMCM/PLL/BUFR can be automatically derived by Vivado without user creation. If the user only wants to change the name of the derived clock, and the rest of the frequency is automatically derived by the tool, just write three opTIons, the rest can not be written: create_generated_clock [-name arg] [-source args] [-master_clock arg] Tools can't automatically derive derived clocks, including dividers built using registers and combinatorial logic, which must be created by the user using create_generated_clock.

In the early stages of design, tools can be focused on meeting the timing requirements within the FPGA without I/O constraints. When the timing requirements are basically met, plus I/O constraints run. The I/O constraints in XDC have the following points to note:

Port timing requirements without any I/O constraints are considered infinite.

Set_input_delay / set_output_delay in XDC corresponds to OFFSET IN / OFFSET OUT in UCF, but the angle of view is reversed. OFFSET IN / OFFSET OUT constrains port timing from the perspective of FPGA internal latency, and set_input_delay / set_output_delay is constrained from a system perspective.

Typical I/O timing, including system synchronization, source synchronization, SDR, and DDR, is available in the XDC templates for the Vivado graphical interface. There is also a TIming Constraints Wizard available after the 2014.1 release.

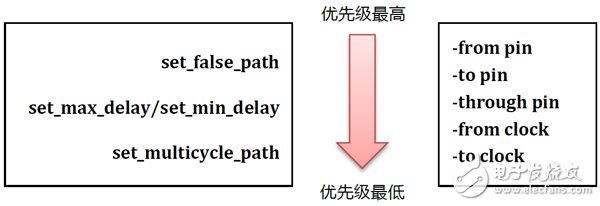

Timing exception constraintTiming exception constraints include set_max_delay/set_min_delay, set_mulTIcycle_path, set_false_path, etc. These constraints are subject to their own priority, in addition to the priority order of the XDC. A general principle is that for the same path, the more specific the priority of the constraint target description, the higher the priority. The different timing exception constraints and the precedence of different conditions in the same constraint are as follows:

For example, the following two XDCs are executed in sequence, and although the second one is executed last, the tool still determines that 15 of the first constraint setting is the max delay value of the path between clk1 and clk2.

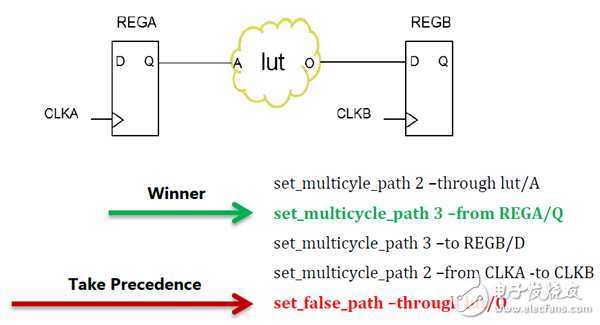

For another example, the following four timing exception constraints are sequentially performed on the illustrated path, and the winner will be the second. However, if you add the last constraint, the false path has the highest priority and will replace all previous timing exception constraints.

The constraint is ultimately to design the service, so to use XDC requires a deep understanding of the circuit structure and design requirements. Next, we will take the example of the clock structure in the common FPGA design to elaborate the XDC constraint skills.

48V30Ah Lithium Ion Battery,Long Cycle Life 48V 30Ah Battery,48V 30Ah Battery For Vehicle,Deep Cycle Life Battery

Jiangsu Zhitai New Energy Technology Co.,Ltd , https://www.zhitainewenergy.com