1. Introduction

In recent years, the field of embedded development has experienced significant growth, and traditional event-triggered programming methods based on the 51-chip's polling loop have become insufficient for meeting modern enterprise requirements for stability and security. Currently, embedded system software includes operating systems such as VxWorks, Linux, WinCE, and μC/OS-II. However, due to cost and technical constraints, microcontrollers often do not support these complex systems. In real-world applications, multiple peripherals and tasks often need to be handled simultaneously, making task scheduling an essential component. This is where time-triggered embedded systems prove to be both simple and practical.

This paper presents a time-triggered multi-task scheduler designed for the AVR microcontroller and implemented in practice. The scheduler uses messages to trigger context switches between different tasks and devices, improving system responsiveness and reliability.

2. Structure Characteristics of AVR Microcontroller

The AVR series, using the ATmega128 as an example, is known for its Harvard architecture, RISC instruction set, low power consumption, and rich on-chip resources. These features significantly simplify peripheral circuits and enhance system stability and reliability. The robust design of the AVR microcontroller provides a solid hardware foundation for embedded system development.

3. Comparison of Two Embedded Trigger Modes

In embedded systems, two primary scheduling approaches are commonly used: event-triggered and time-triggered. Event-triggered systems rely on interrupts, which occur at unpredictable times, while time-triggered systems operate based on a global clock, allowing for predictable behavior in terms of both function and timing.

3.1 Problems with Event Triggering

A common misconception among embedded developers is that interrupt events are never lost, which can lead to serious issues in product development. In reality, interrupt loss is a frequent occurrence in practice. External factors, such as signal loss or excessive frequency, and internal causes, like improper interrupt priority settings or flawed code handling, contribute to this problem.

For example, if an interrupt with high priority is being processed, a lower-priority interrupt may be ignored or delayed, leading to missed responses. When multiple interrupt sources generate signals at random intervals, it becomes nearly impossible to handle all combinations effectively. This increases system complexity and reduces predictability. Studies have shown that even with advanced scheduling algorithms, CPU utilization in event-triggered systems can be very low, limiting their efficiency.

3.2 Advantages of Time Triggering

Time-triggered systems allow designers to process only one event at a time by carefully arranging the execution order. This predictability makes them ideal for safety-critical applications. Kopetz proposed that using a time-triggered cooperative scheduler improves system reliability and reduces CPU and memory usage, making it a more efficient approach for embedded systems.

4. Time-Triggered Embedded System Design

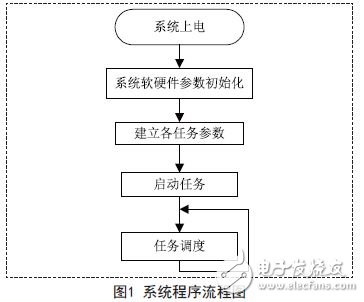

The scheduler in this system separates timer settings from the compiler’s data types and processor bit width, making it easy to adapt to different hardware platforms. The overall system block diagram is shown in Figure 1:

4.1 Message Queue

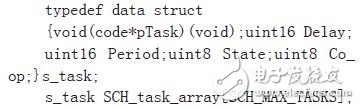

The message queue is the core of the scheduler. It is a user-defined data type that stores information required for each task, typically placed in the DATA area for quick access.

For a time-triggered hybrid scheduler, a specific data structure is used, with a memory overhead of just 8 bytes per task. Even on a 32-bit processor, the overhead remains low at 14 bytes per task.

4.2 Scheduler Timer Initialization Function

This function generates a timing reference to drive the scheduler. The ATmega128 microcontroller selected in this paper has four timers (two 8-bit and two 16-bit), any of which can be used to implement the scheduler.

Void SCH_Init_T0(void) { Delete each task one by one; stop timer 0; set time size function; enable timer 0 mode; start timer 0; }

Note: During initialization, global interrupts must be disabled. For example, SREG = 0x80 or SEI(); the scheduler must first define a default time slice. Choosing an appropriate time slice is critical. If it's too long, the system may not respond quickly enough to interactive events. If it's too short, the scheduler will spend more time switching tasks, reducing efficiency.

Based on experience, a time slice slightly longer than the typical interaction time is preferred. This ensures most tasks complete within one time slice. After testing, a time slice between 1 and 5 ms is generally optimal, balancing response speed and task execution time. The exact value depends on the number of tasks and their execution duration.

4.3 Interrupt Service Routine

It is recommended to activate this routine using CTC mode. When a task is ready to run, it waits for its turn. The content of this routine varies depending on the specific task.

4.4 Scheduler Task Add Function

Cixi Xinke Electronic Technology Co., Ltd. , https://www.cxxinke.com